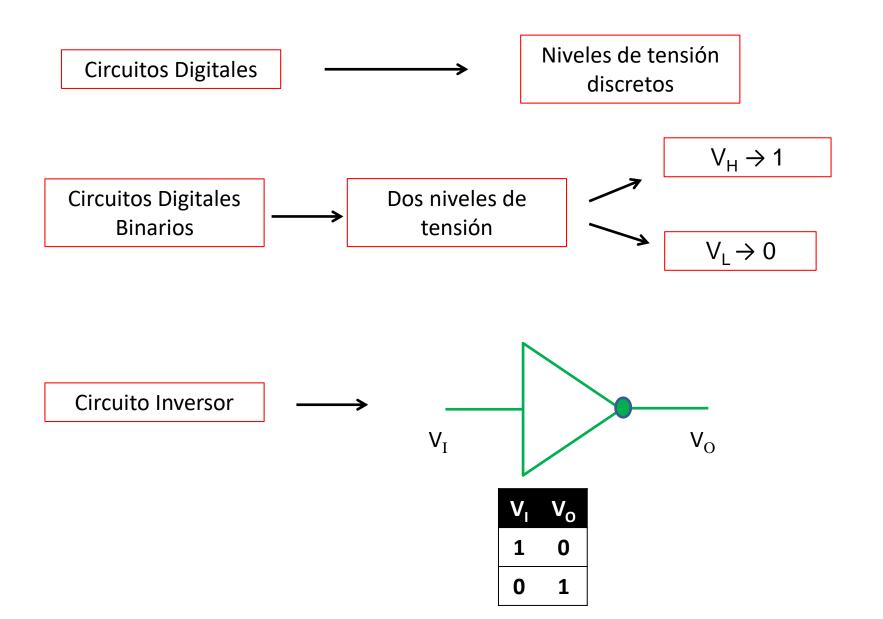

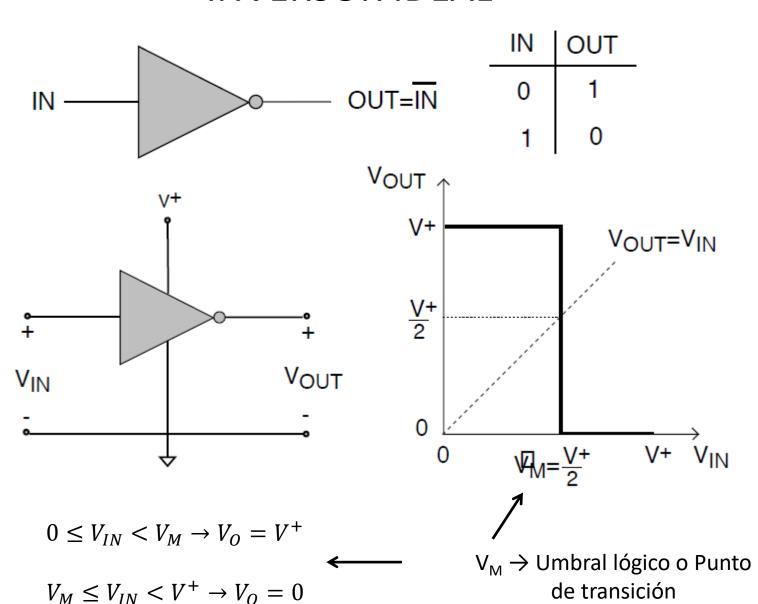

### **INVERSOR IDEAL**

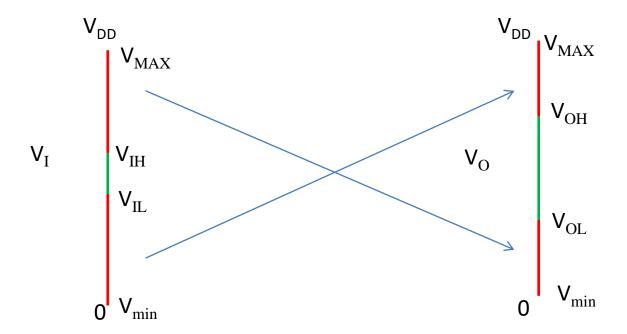

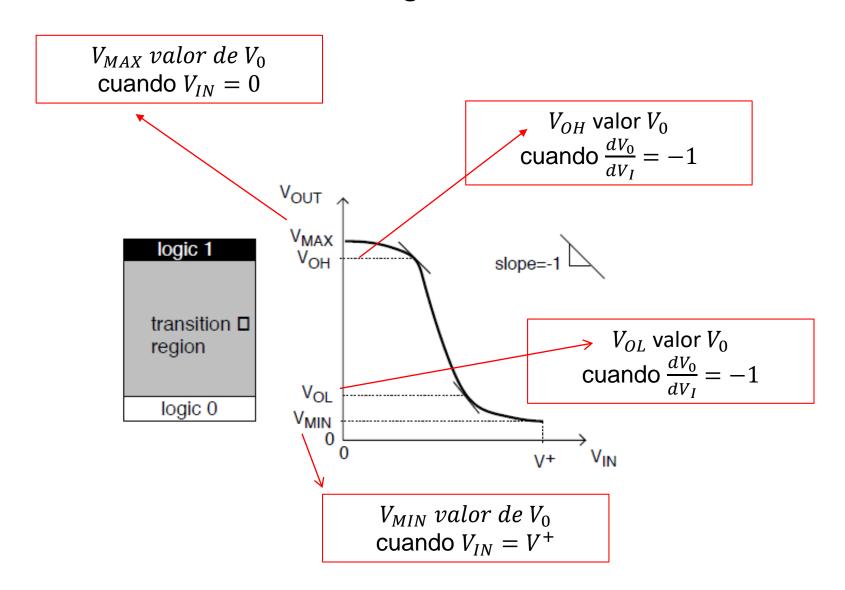

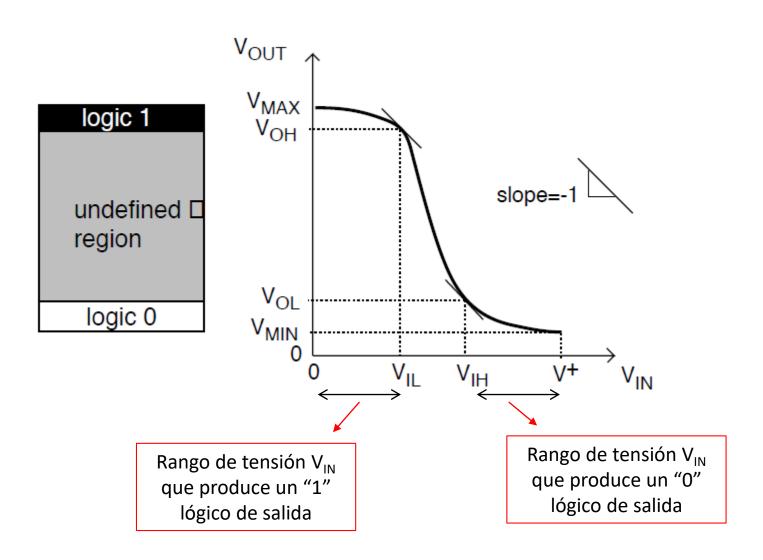

Niveles Lógicos

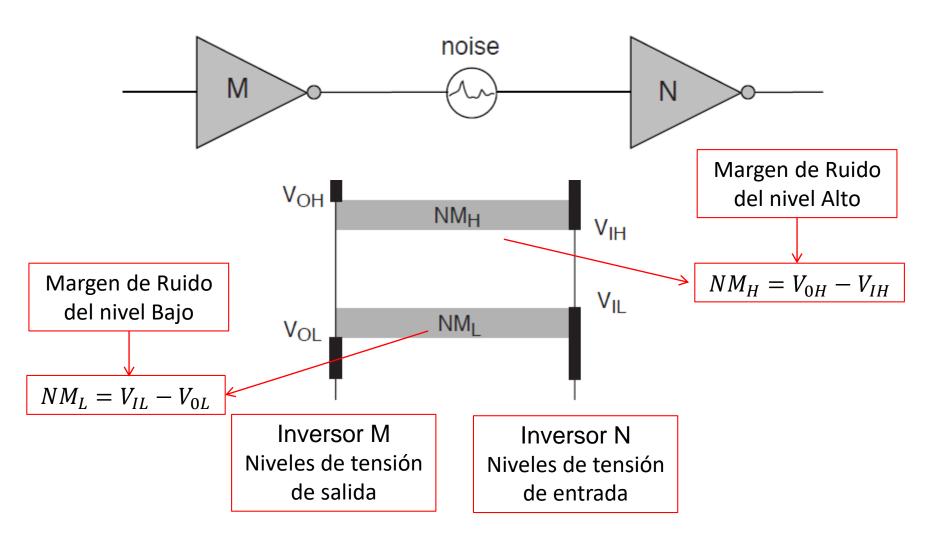

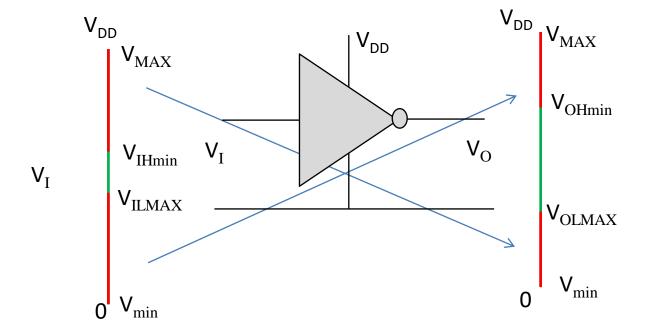

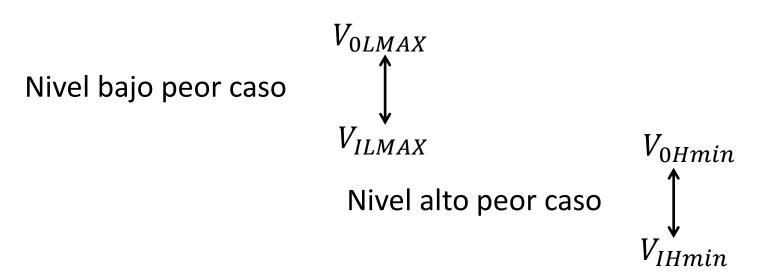

Margen de ruido

El margen de ruido se calcula tomando la peor situación

#### Para conectar dos inversores en cascada

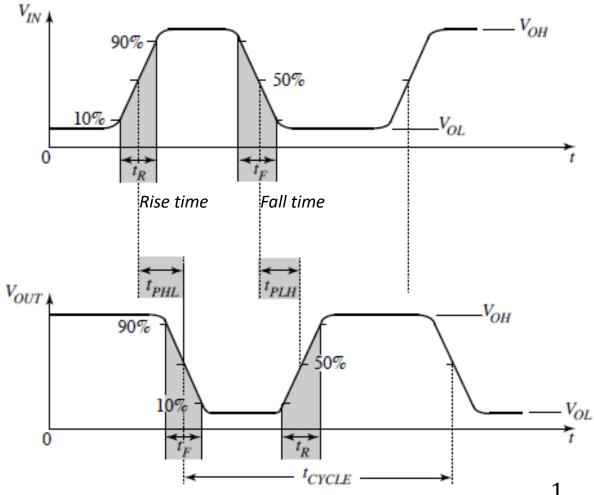

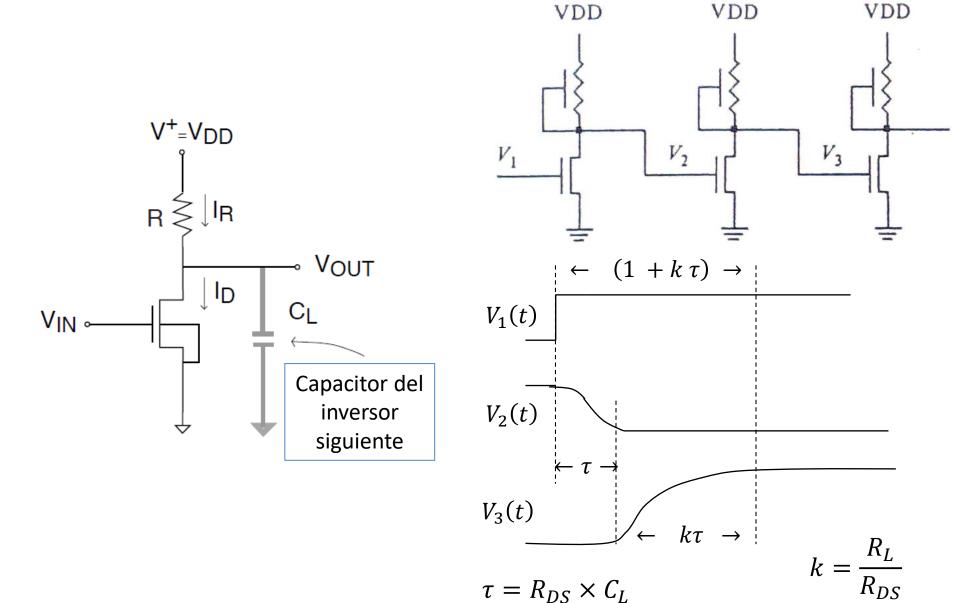

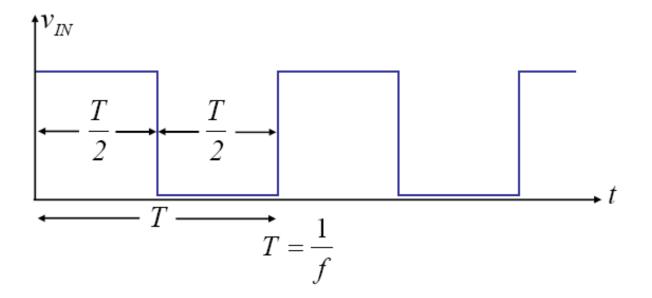

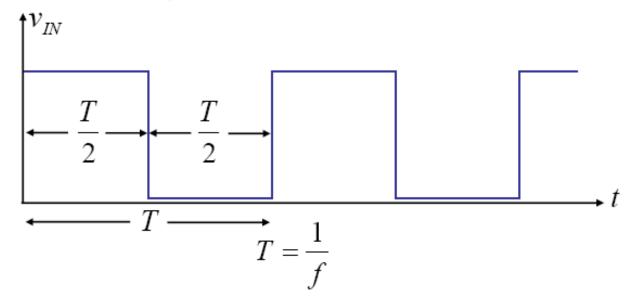

Tiempos de conmutación

$t_{PHL} \rightarrow tiempo\ de\ conmutacion\ de\ alto\ a\ bajo$

$t_{PLH} \rightarrow tiempo\ de\ conmutacion\ de\ bajo\ a\ alto$

$t_P = \frac{1}{2}(t_{PHL} + t_{PLH})$

Retardo de propagación

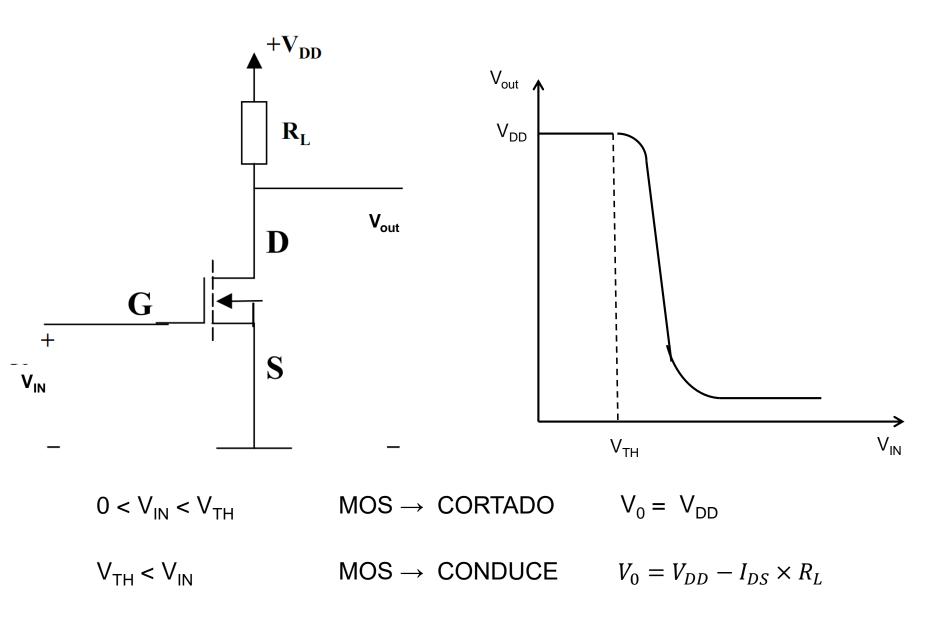

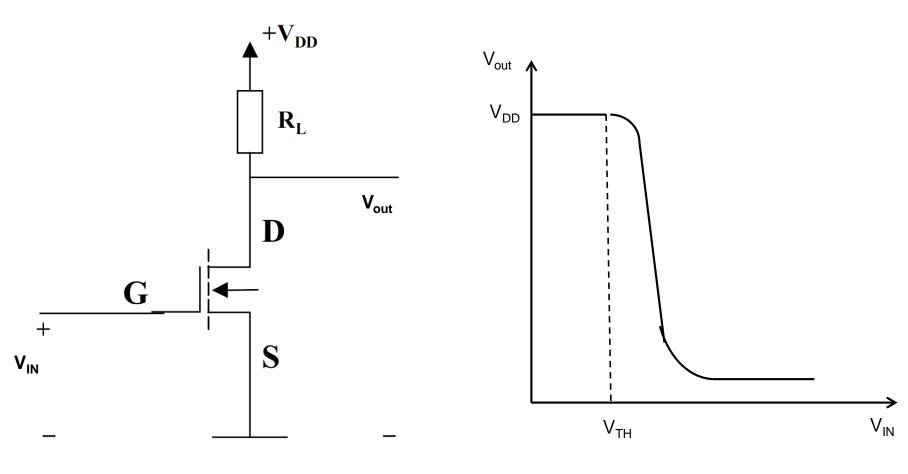

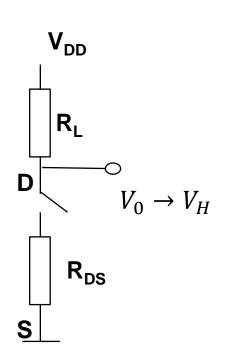

$$0 < V_{IN} < V_{TH}$$

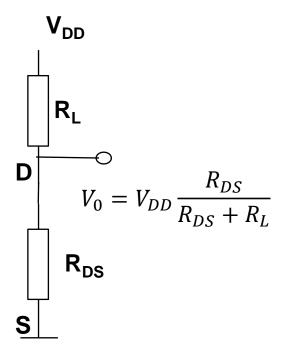

$$V_{TH} < V_{IN}$$

MOS → CORTADO

$MOS \rightarrow CONDUCE$

I<sub>DS</sub> Óhmico o Saturado

$$V_0 = V_{DD} \rightarrow V_H$$

$$V_0 = V_{DD} - I_{DS} \times R_L$$

Resolver desigualdad

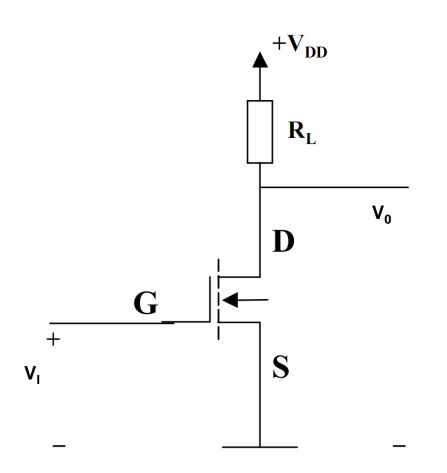

Para  $V_I \leq V_{TH}$

MOS no conduce → llave abierta

$$V_0 = V_{DD} \rightarrow V_{HMAX} = V_{DD}$$

Para  $V_{TH} \leq V_{I}$

MOS conduce → llave cerrada

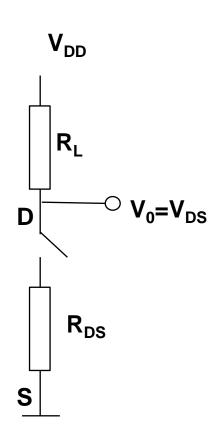

Para  $V_1 = V_{DD}$  si el MOS esta en zona óhmica

$$V_0 = V_{DD} \frac{R_{DS}}{R_{DS} + R_L}$$

$R_{DS} = \frac{1}{\beta (V_{DD} - V_{TH})}$

$$R_{DS} = \frac{1}{\beta(V_{DD} - V_{TH})}$$

$$V_{\text{MAX}} = V_{\text{DD}}$$

$$V_{\text{MAX}} = V_{\text{DD}}$$

$$V_{\text{MAX}} = V_{\text{DD}}$$

$$V_{\text{MIN}} = \frac{V_{DD}}{1 + R_L \beta (V_{DD} - V_{TH})}$$

$$V_{\text{MIN}} = \frac{V_{DD}}{1 + V_{DD}}$$

Para que el nivel de salida bajo sea próximo a cero

$$V_{MIN} = V_{DD} \frac{R_{DS}}{R_{DS} + R_L}$$

$R_L \gg R_{DS}$   $V_{MIN} \approx V_{DD} \frac{R_{DS}}{R_L}$

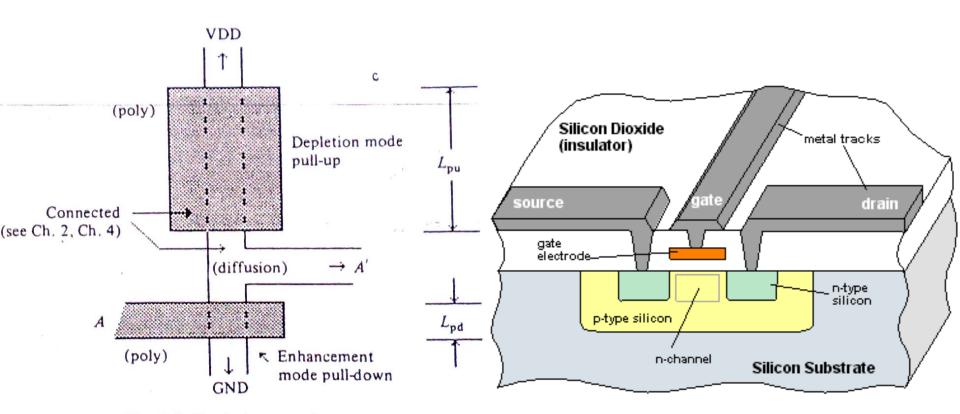

Circuito para obtener R<sub>L</sub> de gran valor con poca área de silicio

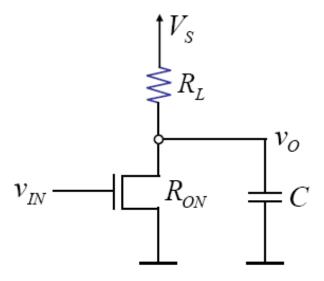

### Retardo del Inversor

# Energía y potencia

# Estudie la disipación de energía en las puertas del MOSFET

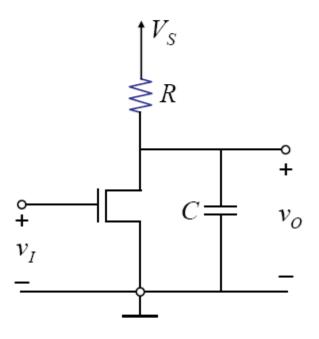

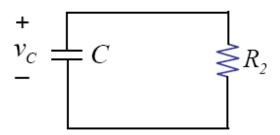

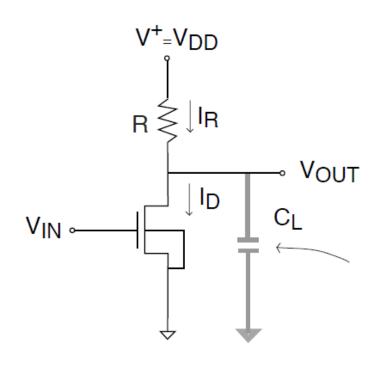

C: capacidad de cableado y  $C_{GS}$  de la puerta siguiente

#### Determinemos:

- la potencia de reserva

- la potencia activa

#### ¿Por qué preocuparnos por la energía?

#### Hoy:

- ¿Cuánto durará la batería?

en modo de reserva

en uso activo

- ¿Se recalentará el chip y se autodestruirá?

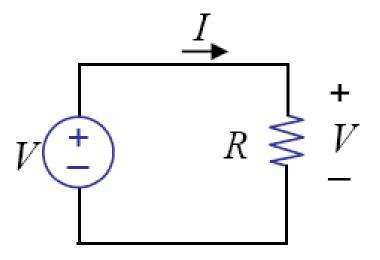

# Ejemplo 1:

Potencia,

$$P = VI = \frac{V^2}{R}$$

Energía disipada en tiempo T

$$E = VIT$$

### Para nuestra puerta:

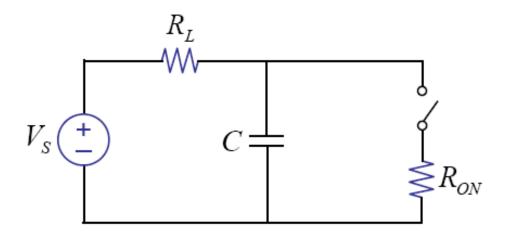

### Ejemplo 2:

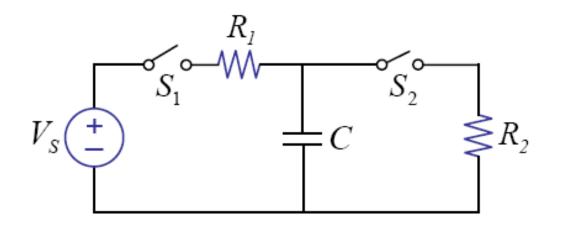

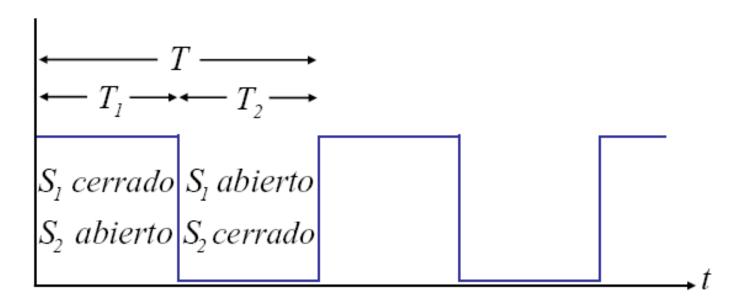

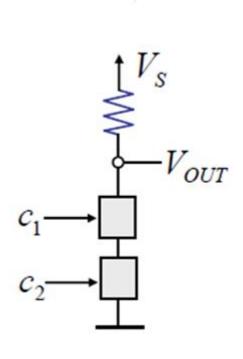

#### Considere:

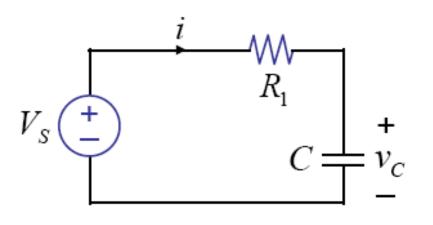

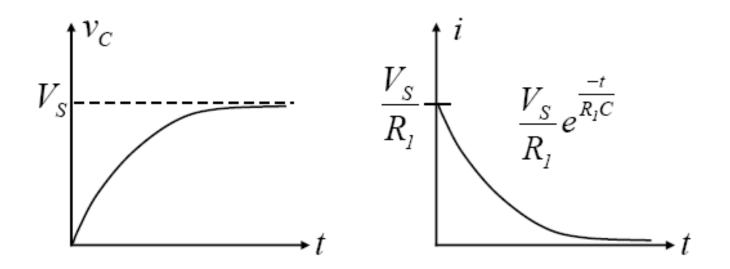

### $T_1$ : $S_1$ cerrado, $S_2$ abierto

suponga que,  $v_C = 0$  en t = 0

#### Energía total que proporciona una fuente durante $T_{I}$

$$E = \int_{0}^{T_{I}} V_{S} i dt$$

$$= \int_{0}^{T_{I}} \frac{V_{S}^{2}}{R_{I}} e^{\frac{-t}{R_{I}C}} dt$$

$$= -\frac{V_{S}^{2}}{R_{I}} R_{I} C e^{\frac{-t}{R_{I}C}} \Big|_{0}^{T_{I}}$$

$$= C V_{S}^{2} \left( 1 - e^{\frac{-T_{I}}{R_{I}C}} \right)$$

$$\approx C \ V_{\rm S}^{\ 2} \ si \ T_{\rm I} >> R_{\rm I} C$$

es decir, si esperamos lo suficiente

$$\frac{1}{2}CV_{S}^{2} \quad almacenado \ en \ C,$$

$$E_{I} = \frac{1}{2}CV_{S}^{2} \quad disipado \ en \ R_{I}$$

Independiente de R

#### $T_2$ : $S_2$ cerrado, $S_1$ abierto

En un principio,  $v_C = V_S$  (recuerde  $T_I >> R_I C$ )

Por lo tanto, inicialmente,

energía almacenada en condensador =  $\frac{1}{2}CV_s^2$

Suponga que  $T_2 >> R_2C$

Por tanto, el condensador se descarga  $\sim$ completamente en  $T_2$ Por tanto, la energía disipada en  $R_2$  durante  $T_2$ ,

$$E_2 = \frac{1}{2}CV_S^2$$

$E_1$ ,  $E_2$  independiente de  $R_2$

### Juntando los dos:

Energía disipada en cada ciclo,

$$E = E_1 + E_2$$

$$= \frac{1}{2}CV_s^2 + \frac{1}{2}CV_s^2$$

$$E = CV_s^2 \quad energia \ disipada \ en$$

$$la \ carga \ y \ descarga \ de \ C$$

Supone que C se carga y se descarga completamente.

### Potencia media,

$$\overline{P} = \frac{E}{T}$$

$$= \frac{CV_S^2}{T}$$

$$= CV_S^2 f$$

frecuencia  $f = \frac{1}{T}$

#### Volvemos a nuestro inversor —

¿Qué es  $\overline{P}$  para la entrada siguiente?

### Circuito equivalente

¿Qué es  $\overline{P}$  para la entrada siguiente?

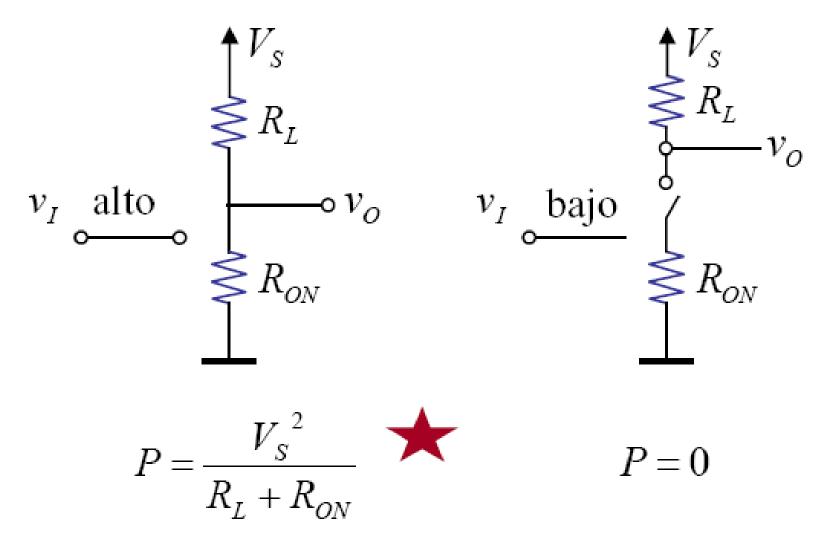

# ¿Qué es $\overline{P}$ para la puerta?

Cuando

$$R_{\!\scriptscriptstyle L}>>R_{\scriptscriptstyle ON}$$

$$\overline{P} = \frac{{V_S}^2}{2R_L} + C{V_S}^2 f$$

En modo de reserva, se puede suponer que la mitad de las puertas en un chip están ON. Por tanto,  $\overline{P}_{EST\acute{A}TICO}$  por puerta es  $V_S^2$ .

Está relacionado con la potencia de reserva.

En modo de reserva,  $f \rightarrow 0$ , por lo que la potencia dinámica es 0

#### Potencia

$$P_{E1} = 0 P_{E2} = \frac{V_I}{R_{DS}}$$

$$P_E = \frac{P_{E1} + P_{E2}}{2}$$

$P_E = \frac{1}{2} \frac{V_{DD}^2}{(R_{DS} + R_L)}$

$$P = P_E + P_D$$

$$P_D = C_L V_{DD}^2 \times f$$

$$P \approx \frac{V_{DD}^2}{2R_L} + C_L V_{DD}^2 \times f$$

### Algunos números...

Un chip con 106 puertas cronometrando a 100 MHZ C = 1 f F $R_L = 10 \, k\Omega$  $f = 100 \times 10^6$  $V_s = 5V$  $\overline{P} = 10^6 \left[ \frac{25}{2 \times 10^4} + 10^{-15} \times 25 \times 100 \times 10^6 \right]$  $=10^6$  [1.25 milivatios + 2.5 microvatios] i **problema!** 1.25KW! 2.5W no está mal  $\alpha V_{\rm s}^{2}$ debe deshacerse de esto  $\alpha f$ reduzca  $V_s$

$5V \rightarrow 1V$

$2.5W \rightarrow 150 \, mW$

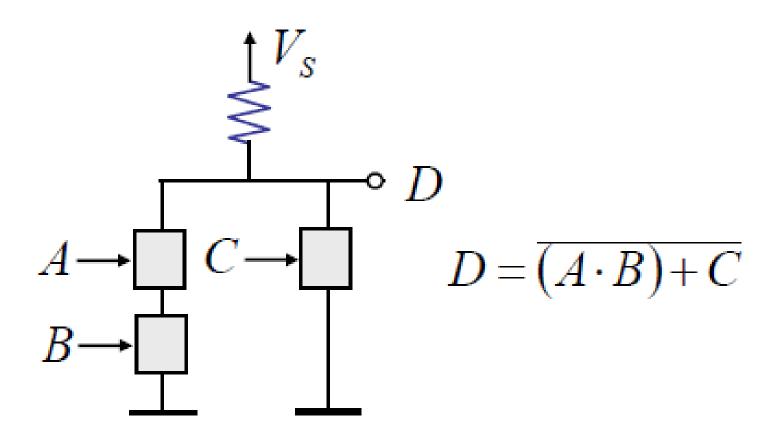

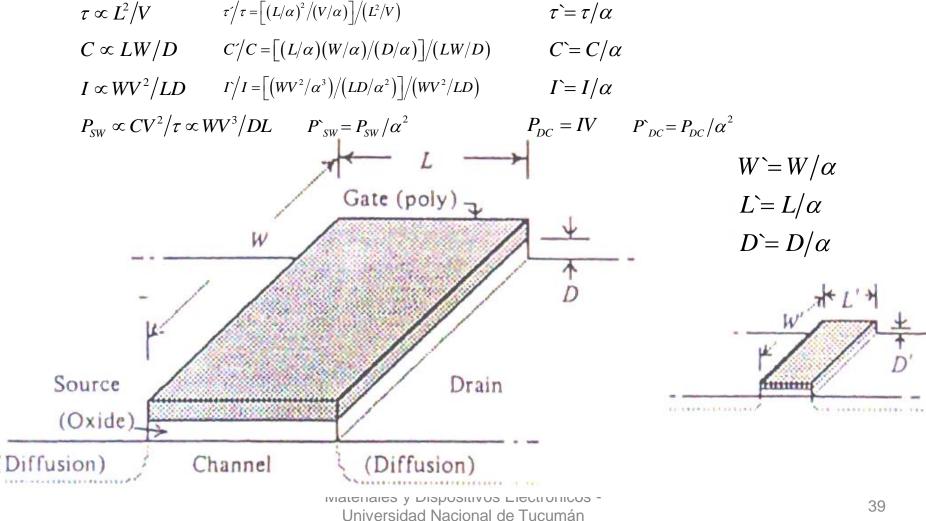

Fig. 1.8 Basic inverter layout.

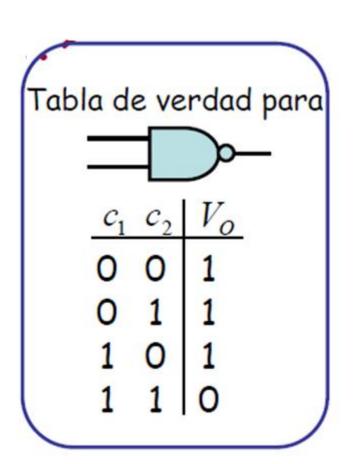

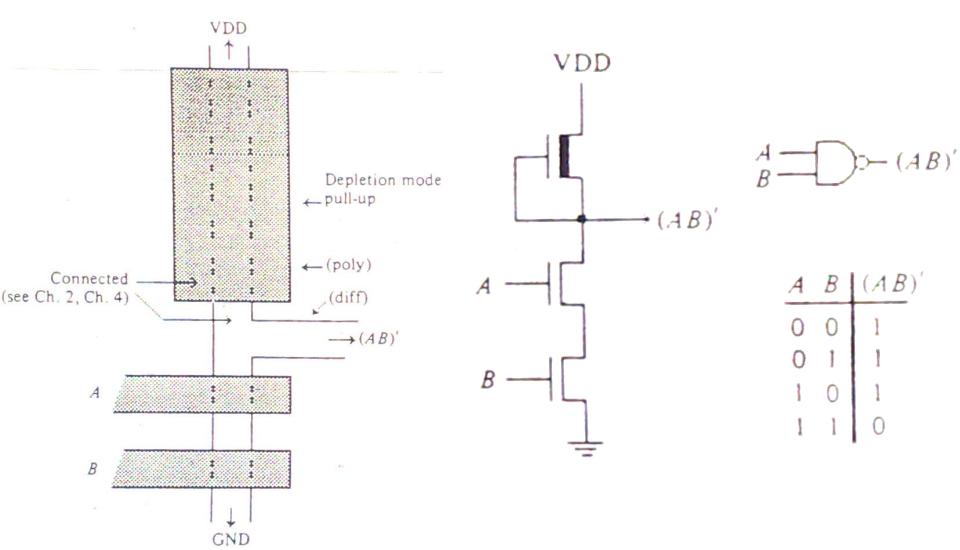

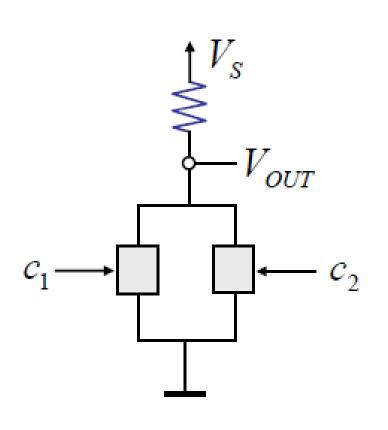

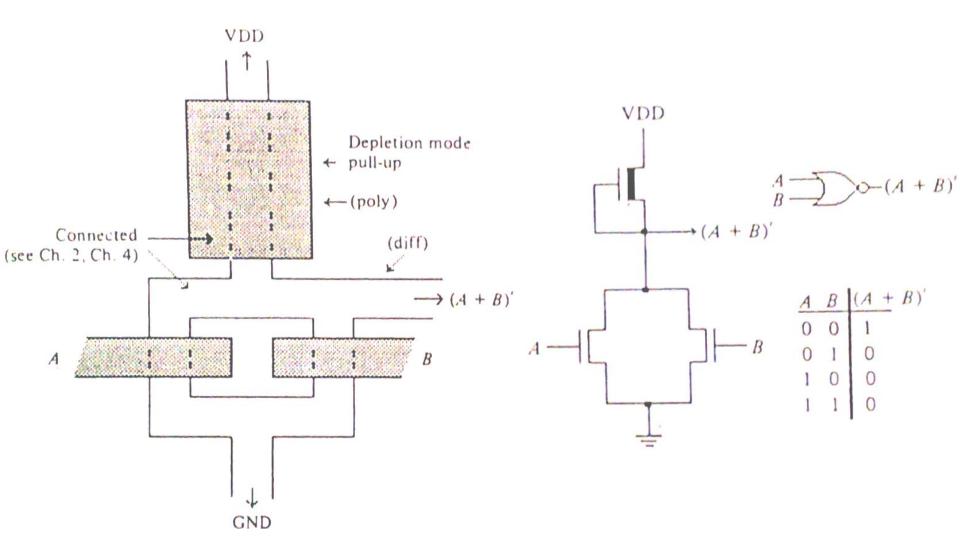

# Compuerta NAND

# Compuerta NAND

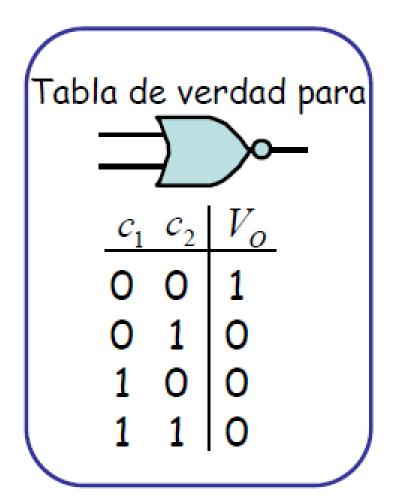

## Compuerta NOR

# Compuerta NOR

### Función LOGICA

# Efectos debido a la miniaturización de los circuitos MOS

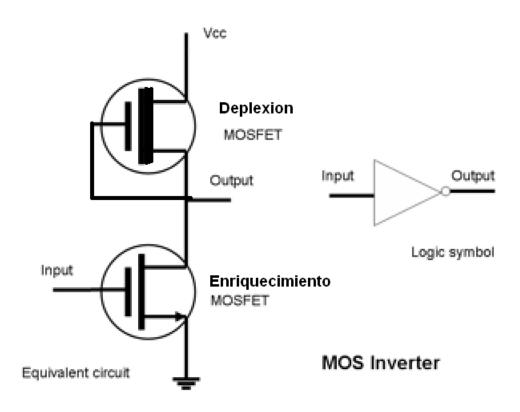

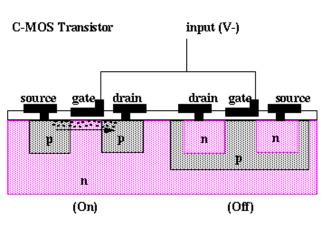

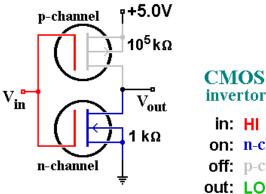

### Aplicaciones: Circuitos Lógicos Tecnología CMOS

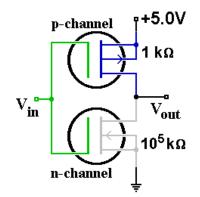

**CMOS** invertor

in: HI on: n-channel off: p-channel

**CMOS** invertor

in: LO

on: p-channel

off: n-channel

out: HI

Inversor (NOT)

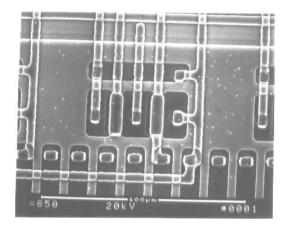

Materiales y Dispositivos Electrónicos -Universidad Nacional de Tucumán

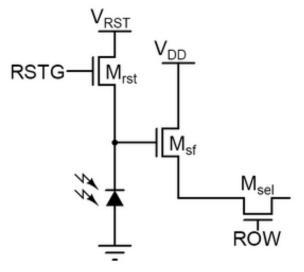

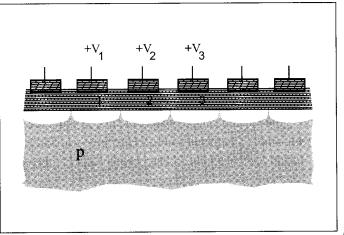

### Aplicaciones: Memorias RAM

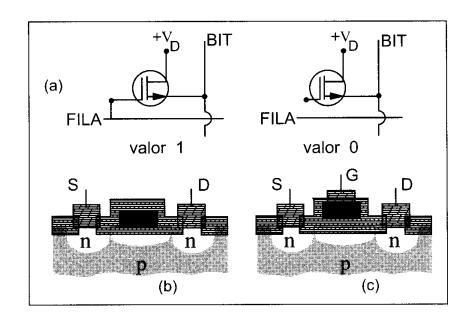

**DRAM**

Se almacena un "1" en la celda cargando el condensador mediante una  $V_G$  en fila y  $V_D$  en bit

La lectura se hace aplicando  $V_{\rm G}$  en fila y midiendo la corriente en la línea bit

La lectura es un proceso destructivo. Hay que restaurar el valor leído

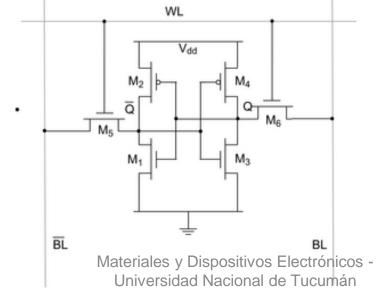

**SRAM**

### Aplicaciones: Memorias ROM

**EPROM**

#### **MOSFET ROM**

## Aplicaciones: CCD

CCD

2.1 x 2.3 mm

**CMOS** sensor